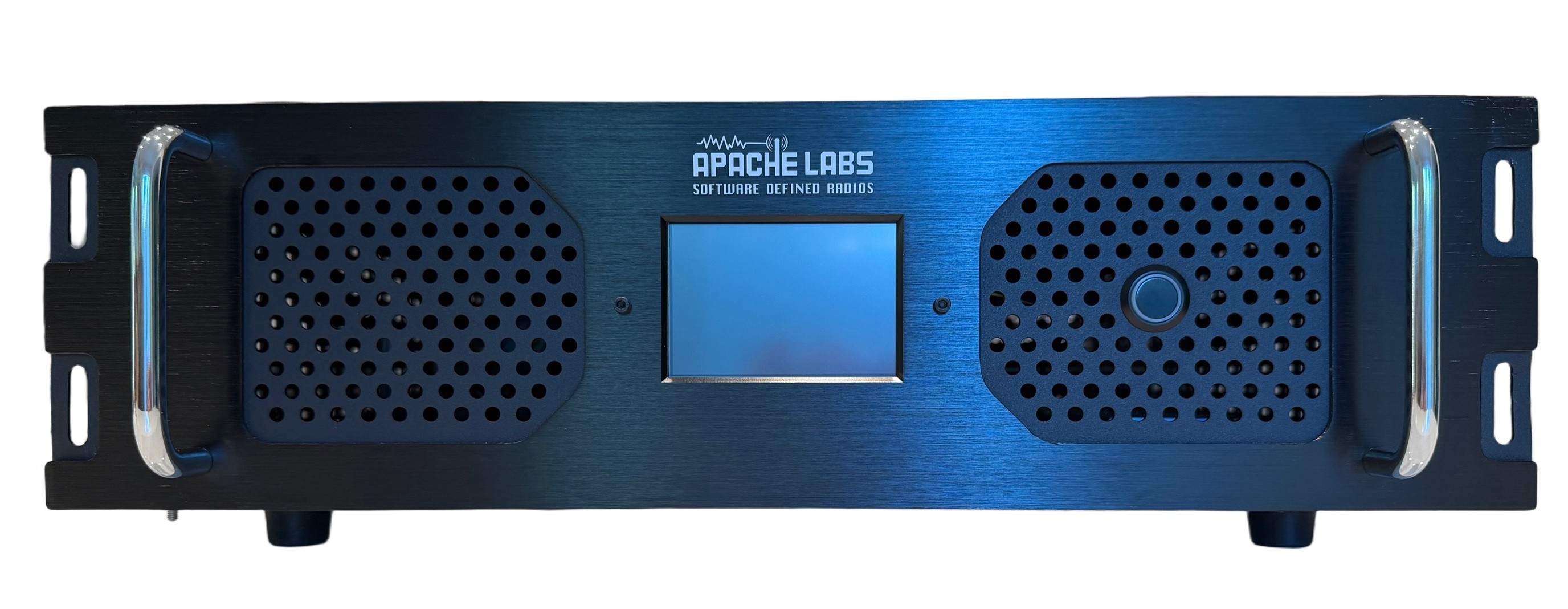

Introducing the ANAN-G1

The ANAN-G1 represents the next evolution in affordable, high-performance Software Defined Radios, building on the proven OpenHPSDR platform and offering seamless compatibility with Thetis software. Designed for operators who demand uncompromising performance without breaking the bank, the G1 delivers exceptional capability in a compact, value-driven package.

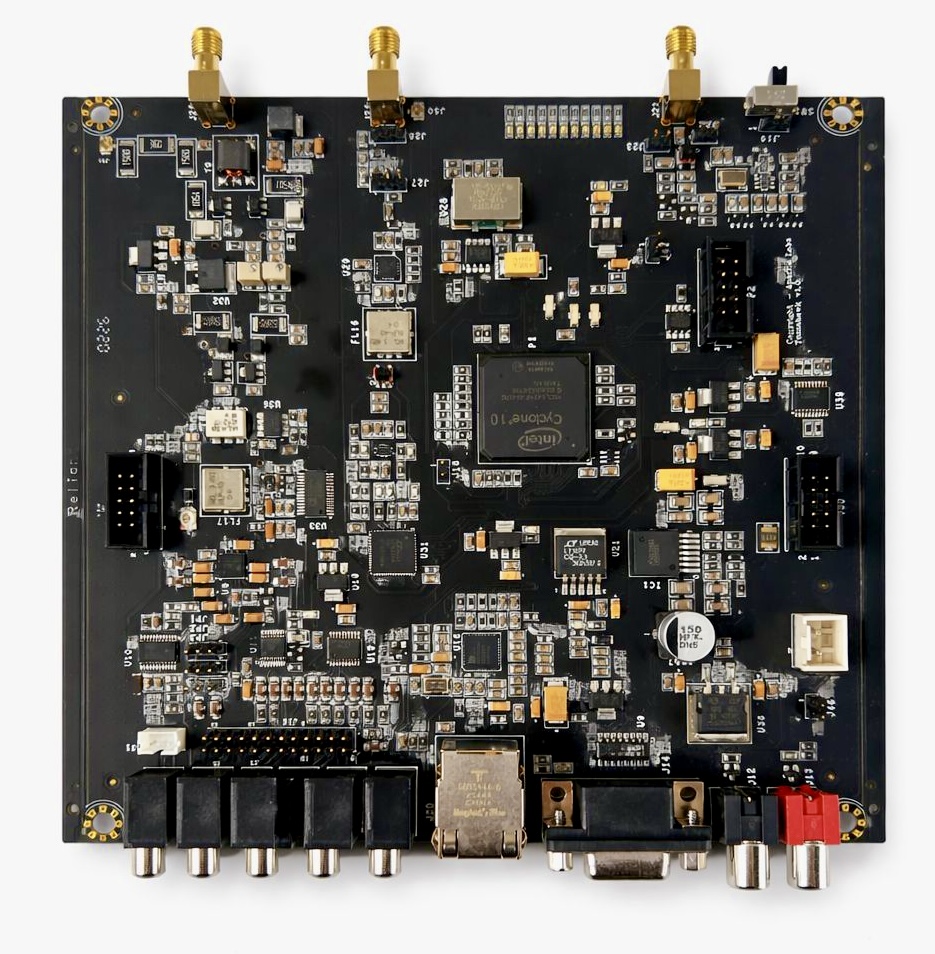

At its core, the ANAN-G1 employs a 16-bit ADC delivering over 100 dB of dynamic range, ensuring clean, distortion-free reception across challenging band conditions. Its architecture is powered by an Intel Cyclone 10 FPGA, providing the horsepower needed for advanced DSP, precision timing, and seamless multi-receiver operation. A high-dynamic-range front end—including a broadcast band (BCB) reject high-pass filter—adds further resilience against strong local signals.

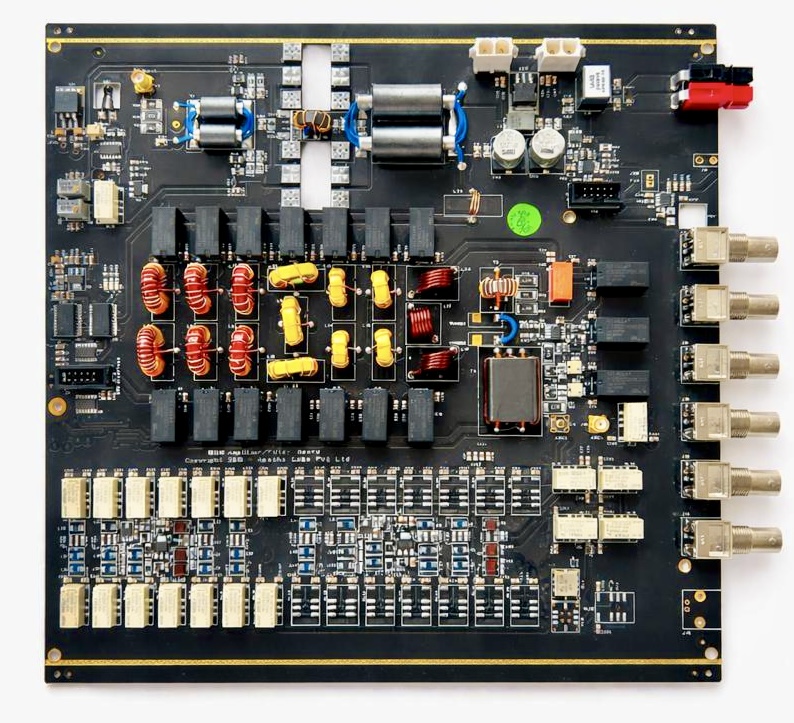

Extensive Band Pass Filtering and 6M High dynamic Range LNA

Advanced features such as a PureSignal feedback input, support for four simultaneous software receivers, and tight Thetis integration put the G1 in a class of its own. Whether you’re chasing weak DX, contesting, or simply enjoying high-fidelity amateur radio, the ANAN-G1 combines cutting-edge performance with exceptional value.

The ANAN-G1 is expected to ship in January 2026 and will be locally manufactured and shipped from California, USA, ensuring faster delivery, reliable service, and long-term support. The promotion price of $1795 applies only to the first 100 orders.

Quite simply, the ANAN-G1 is the best bang for the buck in the entire SDR market.

Technical Specifications

Specifications & Highlights:

- Continuous, uninterrupted, receive coverage from 10KHz to 55MHz.

- 16bit ADC and DAC

- Band Pass Filters and a High Dynamic Range 6M LNA

- Supports 4 fully independent receivers (sharing the same antenna - and with suitable PC software)

- Each receiver can display 48/96/192kHz of spectrum

- Blocking Dynamic Range (ARRL Method) no detectable gain compression below ADC overload

- Transmit and receiver image rejection > 110dB

- Full duplex operation, any split over entire 160m to 6m range.

- Transmitter two-tone 3rd order IMD of -50 to 55dBc on 20m @ 10W PEP

- 100W RF output on 160 – 6m

- Built-in high performance preamp, with a noise floor typically -135dBm in 500Hz

- Software-selectable 31dB input attenuator in 1dB steps

- High performance receiver – (ie Dynamic Range typically 125dB)

- FPGA code can be updated via the Industry Standard TCP/IP network Ethernet connection

- Seven user-configurable open-collector outputs, independently selectable per band and Tx/Rx (for relay control, etc - with sequencing via PC code)

- Microphone PTT jumper-selectable from tip or ring connection

- Bias for electret microphones via jumper

- Operate from a 13.8v DC supply

General Specifications

- Architecture: Direct Sampling DDC/DUC Transceiver

- Power Supply: 13.8 VDC (Power Pole connectors)

- Current Drain: RX: Max 3 A, TX: Max 25 A

- Power Output: Max 100W

- Dimensions: 10.4" W x 3.11" H x 10.87" D

- Weight: 15.8 LB

Receiver Specifications

- Frequency Coverage: 9kHz to 60MHz (specific ranges may vary by version)

- Attenuator: Software-selectable, 1-30dB in 1dB steps

- Dynamic Range: Reciprocal Mixing Dynamic Range (RMDR) of 116dB @ 2kHz offset (MKII)

- High Pass filtering for Broadcast Band Rejection

Transmitter Specifications

- Modes: CW, SSB, NFM, AM, Digital

- Power Output: 100W for CW, SSB, FM, RTTY, and digital modes, 1-30W for AM.

- IMD: Typically < -50dBc on 20m @ 100W PEP

Software & Control

- Interface: Ethernet

- Software: Compatible with OpenHPSDR-based software like Thetis and PiHPSDR

- FPGA: Intel Cyclone 10 LP

Videos and Images

Related Products

Subscribe Newsletter

To get the latest scoop right to your inbox.